## Physics 351: Electronics II Introduction to Digital Circuits

#### Prerequisites: PHYS 252.

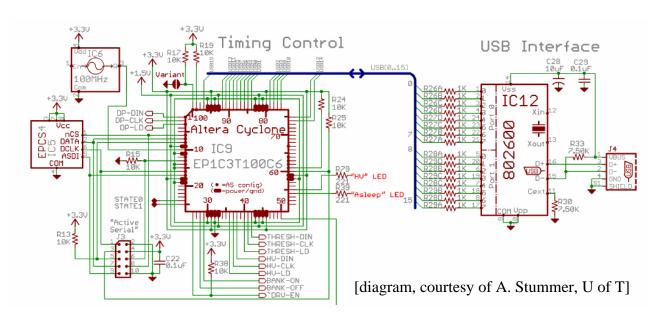

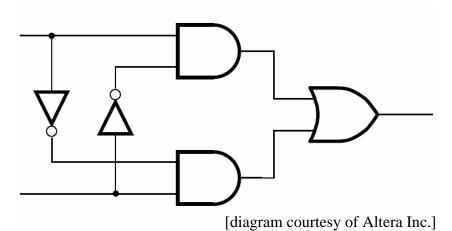

Introduction to digital electronics: Theory, design, and application of digital circuits ... or how to understand and make circuits like these:

Small print: If you don't have any experience with analog electronics you should talk to me after class.

#### Instructors

#### **Prof. Seth Aubin**

Office: room 333 (3rd floor back hall), tel: 1-3545

Lab: room 15 (basement next to machine shop), tel: 1-3532

e-mail: saaubi@wm.edu

web: <a href="http://www.physics.wm.edu/~saubin/index.html">http://www.physics.wm.edu/~saubin/index.html</a>

#### **Aiyana Garcia**

Office: rooms 15 and 307, tel: 1-3532

e-mail: apgarc@wm.edu

#### Office hours (held in room 148):

Monday: 3-4:30 pm (Aubin) Thursday 2-3:30 pm (Garcia)

## **Course Objectives**

**Primary:** Design and test both basic and advanced digital circuits for *digital logic*, *signal acquisition*, and *digital signal processing*.

**Secondary:** Learn experimental research skills.

#### **Covered topics:**

- Binary numbers, logic gates, and Karnaugh maps.

- Memory, flip-flops, and clocked latches.

- Clocks, timing, and one-shots.

- Counters, registers, and state machines.

- Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC).

- Optical and magnetic isolation.

- Field Programmable Gate Arrays (FPGA).

- Verilog language FPGA programming.

- Digital Signal Processing (DSP).

## **FPGAs for Physicists**

#### Field Programmable Gate Array (FPGA) chips for physicists

- Contain 10,000-100,000 logic gates + memory.

- Rerogrammable via a computer (Quartus II v7.1).

- Stand alone circuitry (with flash memory).

- Parallel processing.

Please request a license from Altera Inc.

(see course webpage for the necessary internet links)

Note: Quartus II is available on lab computers and in room ??? of Swem library.

## **DSP design project (I)**

A central component of the course is an FPGA-based digital signal processing (DSP) project. The general guidelines for the projects are:

- > Teams of 2-3 students (depends on lab section distribution).

- ➤ Each team has a budget of \$250 USD.

- All teams have the same project.

- This section of the course is a design and construction competition.

The purpose of the one month team project is to help you develop practical digital circuit design skills, as well as the following more general research skills:

- Complex device design.

- Project budgeting.

- Formal project proposal writing.

- Finding, selecting, and purchasing device components.

- Device construction.

- Troubleshooting and debugging.

- Oral and web presentations of the device.

## **DSP design project (II)**

- ➤ The project will be based on an FPGA.

- The specific project requirements will be announced next week.

- ➤ The project is the most important part of the course.

- > It will be graded according to the following weights:

| Total                        | 60% |

|------------------------------|-----|

| Project lab book and wiki    | 5%  |

| Web presentation of device   | 5%  |

| Oral presentation of device. | 5%  |

| Device performance           | 25% |

| Device construction          | 10% |

| Formal project proposal      | 10% |

## **Evaluation**

Notebooks/Reports: 30%

Quizzes/Participation: 10%

DSP project: 60%

Total = 100%

Note: There is no final exam for the course

#### **Due Dates**

#### Lab books

In addition to lab notes, the lab books should include all design exercises.

Lab books are due by 5pm 2 days after lab & will be returned by the next lab period:

- → Thursdays for the Tuesday section

- → Fridays for the Wednesday section

#### > Reports

- Reports are due on monday the following week.

- Instructor will indicate for which labs a report is due.

- You can expect 2-3 reports for the semester.

- Lab books should not be turned in when lab report is due.

- Important measured numbers should include an estimated uncertainty.

## Schedule (I)

Week 0: 8/27-29 NO CLASS

Week 1: 9/3-5 Digital Logic

Class & lab: Binary numbers, logic gates, Karnaugh maps.

Week 2: 9/10-12 Introduction to FPGAs

Class & lab: FPGAs, Verilog programming language, applications

Week 3: 9/17-19 Memory

Class & lab: Memory, flip-flops, clocked latch.

Week 4: 9/24-26 Timing

Class & lab: Clocks, timing, one-shots.

Week 5: 10/1-3 State Machines

Class & lab: Counters, registers, state machines I.

Week 6: 10/8-10 Complex Digital Circuits

Class & lab: State machines II, synchronous counters, and sequencing.

Week 6.5: 10/17 Wednesday lab group jumps one week ahead

Class: No class; Lab: Project.

## Schedule (II)

Week 7: 10/22-24 Analog-Digital Interfacing

Class & lab: Analog-to-digital converters, digital-to-analog converters, digital isolation.

**Project:** Formal project proposals are due October 26, 2007.

Week 8: 10/29-31 Digital Signal Processing

Class & lab: FPGAs for digital signal processing.

**Project:** project funds are released.

Week 9: 11/5-7 Project week 1

Class: Microprocessors and FPGAs I (tentative)

Lab & Project: Project construction begins.

Week 10: 11/12-14 Project week 2

Class: Microprocessors and FPGAs II (tentative)

Lab & Project: Project construction continues.

## Schedule (III)

Week 11: 11/19-20 Project week 3

Class: Microprocessors and FPGAs III (tentative)

Lab & Project: Project construction continues.

Tuesday and Wednesday lab groups equalize schedules

Class: Microprocessors and FPGAs IV (tentative)

Lab & Project: Project debugging and troubleshooting.

Week 13: 12/3-5 Project week 5

Class: Oral presentations and website launch.

Lab & Project: Device performance testing and review.

# Introduction to Digital Logic

## **Digital Variables**

A digital circuit has only 2 possible values HIGH (H or 1) and LOW (L or 0)

- → Does not need to be precision designed.

- → Not very sensitive to electronic noise.

Here are a few voltage-logic conventions:

| Convention | Supply    | LOW          | HIGH         | Speed   |

|------------|-----------|--------------|--------------|---------|

| TTL        | + 5 V     | < 0.7 V      | > 2.0 V      | ~5 nS   |

| LVTTL      | + 3.3 V   | < 0.7 V      | > 2.0 V      | ~5 nS   |

| CMOS       | + 3-15 V  | < 20% Supply | > 80% Supply | ~10 nS  |

| GaAs       | undefined | undefined    | undefined    | ~100 pS |

## Digital vs. Analog

#### Digital

- Easy to design (linear logic flow).

- → No feedback!

- Insensitive to electronic noise.

- Easy to design and make very complex circuits.

- Insensitive to specific components.

- Reliable isolation circuitry.

- Tends to consume a lot of power.

- Slower than analog equivalent.

- ➤ Very bad if a single bit is corrupted (std. error rate 1 part per 10¹0).

- → Error correction is important.

#### **Analog**

- ➤ Harder to design and read a circuit, especially with feedback.

- Noise is critical.

- Complex circuits are hard to design.

- > Sensitive to specific components and quality of assembly.

- > Isolation circuitry reduces accuracy.

- Very fast.

- Can be low power.

- > Some circuits must be analog.

## **Transistor-Transistor-Logic (TTL)**

In this course, we will use almost exclusively the TTL family of logic chips.

#### Characteristics:

- Very reliable.

- Widely available.

- Silicon-based with bipolar transistors.

- ➤ Supply: + 5 V, High > 2 V, Low < 0.7 V

- ➤ 1 output can drive 10 inputs (fanout = 10).

- Never leave an input (or output) floating: it will tend to wander between H and L.

CAUTION: If any of your voltages are close to the range 0.7 - 2.0 V, then you should check your circuit and the components.

## **Boolean Operators**

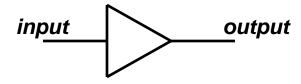

#### **Identity**

1 input  $\rightarrow$  1 output

0 input  $\rightarrow$  0 output

(also called a buffer)

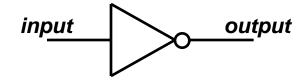

#### <u>Inverter</u>

1 input  $\rightarrow$  0 output

0 input  $\rightarrow$  1 output

Note: Boolean (adj.) refers to something that is 2-valued (named after G. Boole, 1815-1864).

## 2-input operators

#### **AND**

- → Outputs H only if both inputs are H.

- → Written as a product: Y=AB

| INPUTS |   | OUTPUT |

|--------|---|--------|

| А В    |   | AB = Y |

| L      | L | L      |

| L      | Н | L      |

| Н      | L | L      |

| Н      | Н | Н      |

#### <u>OR</u>

- → Outputs H only if either input is H.

- → Written as a sum: Y=A+B

| INP | UTS | OUTPUT  |

|-----|-----|---------|

| Α   | В   | A+B = Y |

| L   | L   | L       |

| L   | Н   | н       |

| Н   | L   | Н       |

| Н   | Н   | Н       |

## **More operators**

### NAND NOR

| Α |  | v |

|---|--|---|

| В |  | • |

| INPUTS |   | OUTPUT              |

|--------|---|---------------------|

| А В    |   | $\overline{AB} = Y$ |

| L      | L | Н                   |

| L      | Н | Н                   |

| Н      | L | н                   |

| Н      | Н | L                   |

| INF | PUTS | OUTPUT             |

|-----|------|--------------------|

| А В |      | <del>A+B</del> = Y |

| L   | L    | Н                  |

| X   | Н    | L                  |

| Н   | X    | L                  |

X = don't care (H or L)

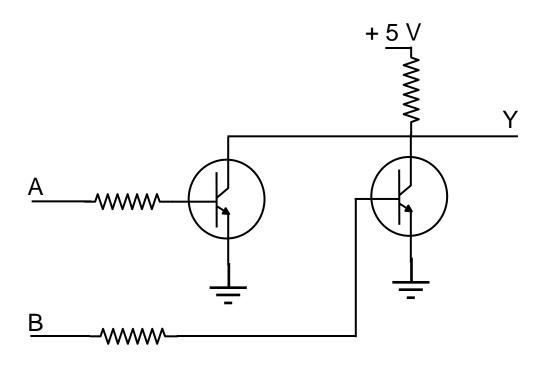

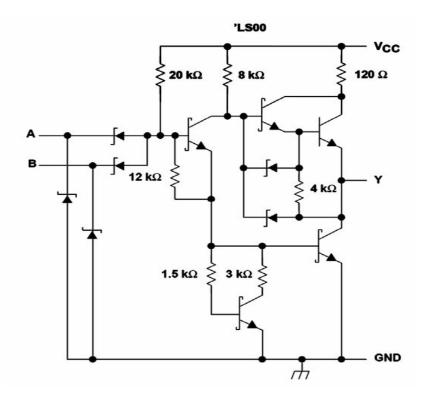

## A little bit of analog

Analog realization of a NOR gate

| INF | PUTS | OUTPUT             |

|-----|------|--------------------|

| Α   | В    | <del>A+B</del> = Y |

| L   | L    | Н                  |

| Х   | Н    | L                  |

| Н   | X    | L                  |

## **Boolean logic identities**

#### <u>Associative</u>

$$ABC = (AB)C = A(BC)$$

$$ABC = (AB)C = A(BC)$$

$A+B+C = (A+B)+C = A+(B+C)$

#### **Commutative**

$$AB = BA$$

$$A+B=B+A$$

#### **Others**

$$AA = A$$

$$A1 = A$$

$$A0 = 0$$

$$A+A=A$$

$$A+1 = 1$$

$$A + 0 = A$$

$$A + AB = A$$

$$A+BC = (A+B)(A+C)$$

$$A + \overline{A} = 1$$

$$A\overline{A} = 0$$

$$A + \overline{A} B = A + B$$

#### **DeMorgan's Theorem**

$$\overline{A+B} = \overline{A} \overline{B}$$

$$\overline{\mathsf{AB}} = \overline{\mathsf{A}} + \overline{\mathsf{B}}$$

## **Exclusive OR**

#### **XOR**

- → Outputs H if either input is H, but not both.

- → Written as a plus sign with a circle around it: Y=A⊕B

| INP | PUTS | OUTPUT  |

|-----|------|---------|

| А В |      | A⊕B = Y |

| L   | L    | L       |

| L   | Н    | Н       |

| Н   | L    | Н       |

| Н   | Н    | L       |

#### XOR realization

## The NAND and NOR gates

#### **DeMorgan's theorem corollary:**

Any logic gate or operation can be constructed exclusively of NAND gates (or NOR gates).

**Note:** a NAND gate with the inputs tied together is a NOT gate.

## **Hardware**

| Name   | Expression | Inputs       | Part #       |

|--------|------------|--------------|--------------|

| AND    | AB         | 2 (also 3&4) | 74xx08       |

| NAND   | AB         | 2 (also 3&4) | 74xx00       |

| OR     | A+B        | 2 (also 3&4) | 74xx32       |

| NOR    | A+B        | 2 (also 3&4) | 74xx02       |

| Invert | A          | 1            | 74xx04       |

| Buffer | Α          | 1            | 74xx365      |

| XOR    | A⊕B        | 2 (also 3&4) | 74xx86 / 386 |

| XNOR   | Ā⊕B        | 2 (also 3&4) | 74xx266      |

Note: We will use mostly Low Speed TTL (xx = LS).

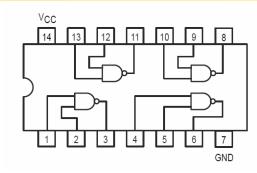

## Example: 74LS00

#### **Quad NAND gate chip**

- > 4 gates per chip.

- Requires + 5 V of power at Vcc.

- Requires a ground connection at GND.

- ➤ Never float an input (i.e. it will wander between 0 and 1).

- ➤ Each gate consists of about 20 components.

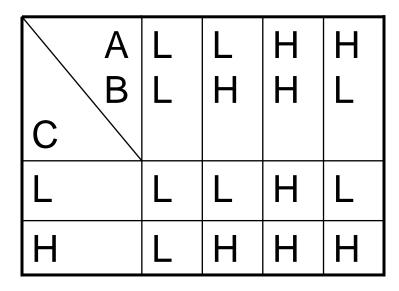

## Karnaugh Maps (I)

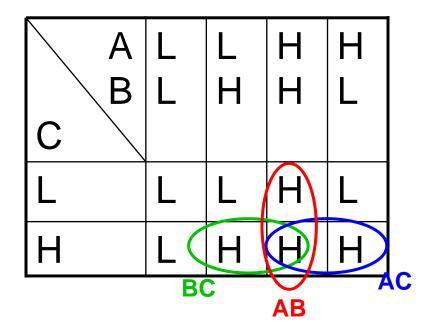

#### Logic table → Karnaugh Map → digital logic circuit

- > Up to 4 inputs, 1 output.

- ➤ Always gives a solution, though not the most efficient one.

#### **Example:**

- 3 person vote.

- 2-person majority produces H output.

| Α | В | С | Q |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

## Karnaugh Maps (II)

- > Arrange inputs on either one of the two table axes.

- ➤ Up to 2 inputs per axis.

- ➤ Order of inputs is important: only one input change per row or column.

## Karnaugh Maps (II)

- Arrange inputs on either one of the two table axes.

- ➤ Up to 2 inputs per axis.

- Order of inputs is important: only one input change per row or column.

- Group together the adjacent "ones": these correspond to AND gates.

- ➤ Alternatively, group adjacent "zeros": these correspond to OR gates.

- Write down the corresponding AND gates: AB, BC, AC

Solution: AB + BC + AC

## Karnaugh Maps (III)

|   | Α | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|

|   | В | 0 | 1 | 1 | 0 |

| С | D |   |   |   |   |

| 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 |

## Karnaugh Maps (III)

|   | Α | 0 | 0 | 1 | 1   |

|---|---|---|---|---|-----|

|   | В | 0 | 1 | 1 | 0   |

| С | D |   |   |   |     |

| 0 | 0 | 1 | 1 | 0 | (1) |

| 0 | 1 | 0 | 1 | 0 | 0   |

| 1 | 1 | 0 | 1 | 1 | 0   |

| 1 | 0 | 1 | 1 | 1 | 0   |

## Karnaugh Maps (III)

|   | Α | 0              | 0            | 1             | 1   |

|---|---|----------------|--------------|---------------|-----|

|   | В | 0              | 1            | 1             | 0   |

| С | D |                |              |               | BC  |

| 0 | 0 | 1              | 1 \\ \bar{A} | 0<br><b>B</b> | (1) |

| 0 | 1 | 0              | 1            | 0             | 0   |

| 1 | 1 | 0<br><b>AD</b> | 1            | 1 B(          | 0   |

| 1 | 0 | 1              | 1            | 1             | 0   |

Solution:  $\overline{A}B + BC + \overline{A}D + \overline{B}\overline{C}\overline{D}$

## **Binary Numbers**

#### Base 10 (i.e. decimal numbers)

$$73691 = 1 \times 10^{0} + 9 \times 10^{1} + 6 \times 10^{2} + 3 \times 10^{3} + 7 \times 10^{4} = 73691_{10}$$

We can represent any integer in a digital circuit if we use base-2 representation.

#### **Base 2 (i.e. binary numbers)**

$$10011101 = 1 \times 2^{0} + 0 \times 2^{1} + 1 \times 2^{2} + 1 \times 2^{3} + 1 \times 2^{4} + 0 \times 2^{5} + 0 \times 2^{6} + 1 \times 2^{7} = 10011101_{2}$$

$$= 1 + 0 + 4 + 8 + 16 + 0 + 0 + 128 = 157_{10}$$

## **Binary Numbers**

#### Base 10 (i.e. decimal numbers)

$$73691 = 1 \times 10^{0} + 9 \times 10^{1} + 6 \times 10^{2} + 3 \times 10^{3} + 7 \times 10^{4} = 73691_{10}$$

We can represent any integer in a digital circuit if we use base-2 representation.

#### **Base 2 (i.e. binary numbers)**

$$1001 \bigcirc 101 = 1 \times 2^{0} + 0 \times 2^{1} + 1 \times 2^{2} + 1 \times 2^{3} + 1 \times 2^{4} + 0 \times 2^{5} + 0 \times 2^{6} + 1 \times 2^{7} = 10011101_{2}$$

$$1-bit = 1 + 0 + 4 + 8 + 16 + 0 + 0 + 128 = 157_{10}$$

$$8-bits = 1 \text{ byte}$$

## **Binary Numbers**

#### Base 10 (i.e. decimal numbers)

$$73691 = 1 \times 10^{0} + 9 \times 10^{1} + 6 \times 10^{2} + 3 \times 10^{3} + 7 \times 10^{4} = 73691_{10}$$

We can represent any integer in a digital circuit if we use base-2 representation.

#### **Base 2 (i.e. binary numbers)**

$$1001 \bigcirc 101 = 1 \times 2^{0} + 0 \times 2^{1} + 1 \times 2^{2} + 1 \times 2^{3} + 1 \times 2^{4} + 0 \times 2^{5} + 0 \times 2^{6} + 1 \times 2^{7} = 10011101_{2}$$

$$1-bit = 1 + 0 + 4 + 8 + 16 + 0 + 0 + 128 = 157_{10}$$

$$8-bits = 1 \text{ byte}$$

#### **Base 16 (i.e. Hexadecimal numbers)**

## Decimal -> Binary

- > To convert from decimal to binary

- → Divides by 2 repeatedly & write the remainders

- ➤ To convert 13<sub>10</sub> to binary

```

13/2 = 6 remainder 1

```

$$6/2 = 3 \text{ remainder } 0$$

$$3/2 = 1$$

remainder 1

$$1/2 = 0$$

remainder 1

> The digits come out in right to left order

$$\rightarrow$$

13<sub>10</sub> = 1101<sub>2</sub>

## **Binary Addition**

> Examples

$$0101_2 + 0010_2 = 0111_2$$

$0101_2 + 0001_2 = 0110_2$

$0111_2 + 0001_2 = 1000_2$

- Differences between decimal & binary addition...

- ➤ In binary we, on average, carry half the time.

- There are only a limited number of possible operands & resultants (1s or 0s).

- Makes digital implementation fairly simple.