### **DSP Project: Lock-In Amplifier**

... don't worry your's will be smaller and simpler.

# **DSP Project Schedule**

The DSP projects will follow the schedule below:

- **October 8, 2007:** DSP design competition launch (this document is released).

- October 26, 2007: Formal project proposals are due.

**October 29, 2007:** Project proposals are graded and returned.

→ Project funds are released (you should start buying ASAP so that you will have your components by the next lab).

October 29 – November 22, 2007: Project construction.

November 26-30, 2007:

Project debugging.

**December 3, 2007:** Oral presentations and website launch.

**December 4-5, 2007:** Official device performance testing and review.

# **DSP Project Purchases**

> Budget = 250.00 USD per team.

> All purchases will go through the instructor to Sylvia Stout.

> You must provide an internet shopping cart printout with all the part numbers. An electronic version is useful and will help speed up the purchase.

$\succ$  If you buy a part at a local store, then you must keep the receipt and submit it to the instructor.

# **DSP Project: Lab Equipment**

You are encouraged to use the parts in the lab to perfect your design, however your final device should include only new non-lab parts (except wire).

The course will provide Altera USB-blaster cables for programming the FPGA configuration chips in Active Serial mode.

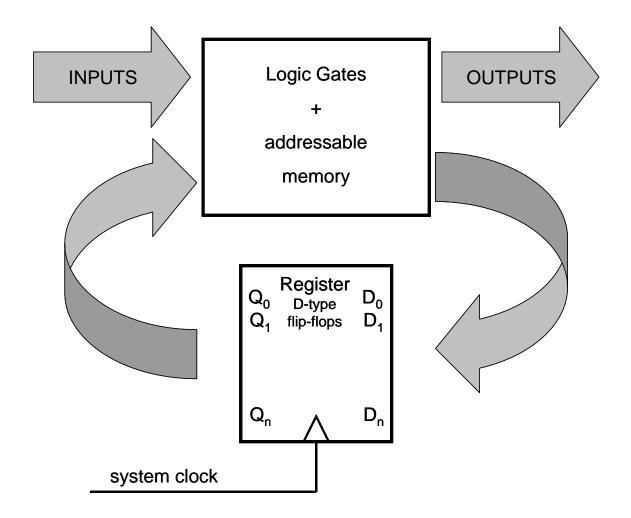

### **State Machine**

Definition: A machine that makes predictable transitions through a sequence of states, based on external inputs and the current state of the machine.

#### **State Machines in Verilog**

```

// Verilog state machine implementation of the divide-by-3 counter

1

module StateMachine v1(clk, reset, out);

2

3

input clk, reset;

// clock and reset declarations

4

// output register declaration

output reg out;

5

6

reg [1:0] state;

// this register holds the state of the machine

7

8

always @(state)

// This always block indicates how the output

9

// should relate to the machine state

begin

10

case (state)

11

2'b00: out = 1'b0;

12

2'b01: out = 1'b1;

13

2'b10: out = 1'b0;

14 //

2'b11: out = 1'b0:

// only required for completeness (not necessary)

11

15

default: out = 1'b0; // default statement guarantees completeness (not necessary)

16

endcase

17

end

18

19

always @ (posedge clk or posedge reset) // This always block constructs the

20

begin

// sequence table

if (reset==1) state = 2'b00;

21

22

else

23

case (state)

24

2'b00: state = 2'b01;

25

2'b01: state = 2'b10;

26

2'b10: state = 2'b00;

27

11

2'b11: state = 2'b00; // only required for completeness (not necessary)

11

28

default: state = 2'b00; // default statement guarantees completeness (not necessary)

29

endcase

30

end

31

endmodule

32

```

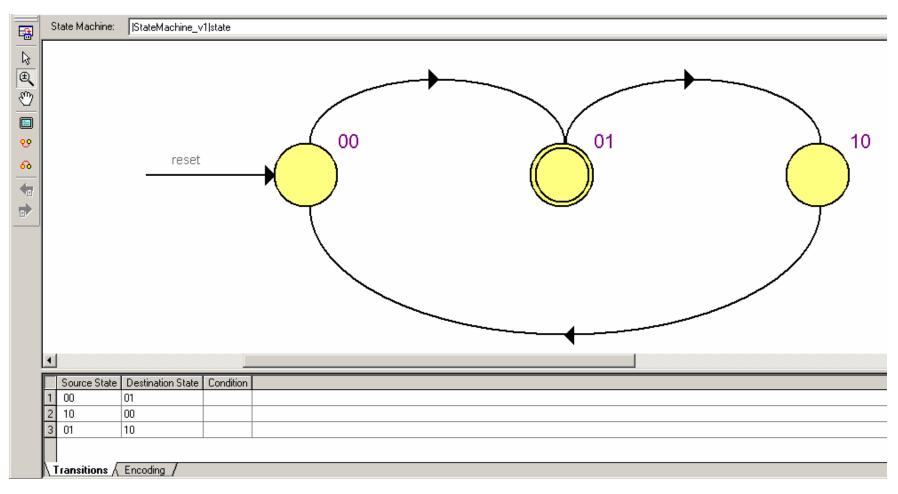

# **State Machines in Quartus II**

Tools > Netlist Viewers > State Machine Viewer

Note: The Quartus II compiler will only find the State Machine if you follow the Verilog example code fairly closely.

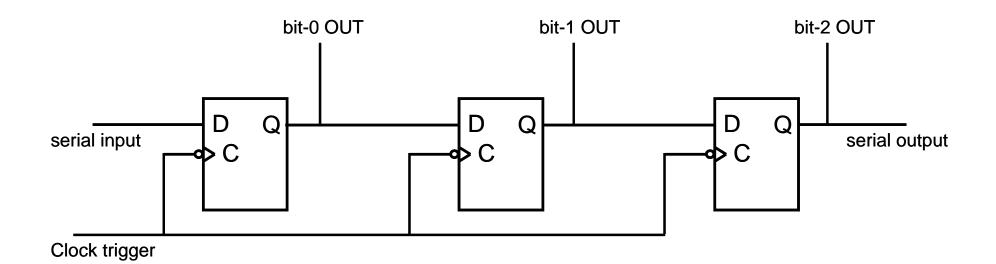

# **Shift Register Circuit**

### **Shift Register in Verilog**

```

module ShiftRegister(serial input, clock, reset, output register, serial output);

1

// serial input line of the shift register

2

input serial input;

3

// clock input line of the shift register

input clock;

4

input reset;

// reset line for resetting the shift register to ZERO

5

output reg [7:0] output register; // Register for the shift register

6

output serial output; // serial output line (equivalent to output register[7])

7

initial

8

begin

9

output register = 8'b00000000; // Start with an empty shift register

10

end

11

12

// connect the serial output line to the bit 8 of the shift register

13

assign serial output = output register[7];

14

15

always 0 (posedge clock or posedge reset)

16

begin

17

if (reset == 1)

18

begin

19

output register <= 8'b0000000; // reset the shift register to ZERO

20

end

21

else

22

begin

23

24

// shifts all the shift register bits to the next bit

25

output register <= output register << 1;</pre>

26

27

// loads the serial input into the first shift register bit

28

output register[0] <= serial input;

29

end

30

end

31

32

endmodule

```

### **Shift Register in Verilog**

```

module ShiftRegister(serial input, clock, reset, output register, serial output);

1

// serial input line of the shift register

2

input serial input;

3

// clock input line of the shift register

input clock;

4

input reset;

// reset line for resetting the shift register to ZERO

5

output reg [7:0] output register; // Register for the shift register

6

output serial output;

// serial output line (equivalent to output register[7])

7

initial

8

begin

9

output register = 8'b00000000; // Start with an empty shift register

10

end

11

12

// connect the serial output line to the bit 8 of the shift register

13

assign serial output = output register[7];

14

always 0 (posedge clock or posedge reset)

15

16

begin

17

if (reset == 1)

18

begin

19

output register <= 8'b0000000;

// reset the shift register to ZERO

20

end

21

else

use the left bit shift operator <<

22

begin

23

24

// shifts all the shift register bits to the next bit

25

output register <= output_register << 1;</pre>

26

27

// loads the serial input into the first shift register bit

28

output register[0] <= serial input;

29

end

30

end

31

32

endmodule

```