#### **Outline**

- 1. DSP project info

- 2. Analog-to-digital converters

- 3. Digital-to-analog converters

- 4. 2-dimensional register memory

### **DSP Project**

Reminder: Project proposal is due Friday, October 26, 2007 by 5pm.

#### Modification of technical specs of lock-in amplifier:

Phase control: 0 to 360° with a resolution of at least (3.6°).

You must be able to shift the phase by exactly 90° from any phase position.

#### Basic guideline for project proposal (also see Project Guidelines document):

You must convince your reader that your design concept will work well enough that it deserves to be funded. This means that your design has reached the point that you can draw up a budget. Your proposal must include a budget which is as specific as possible and an expected timeline.

# Analog $\leftarrow \rightarrow$ Digital

As physicists, we know that:

- > We live in an **analog** world of continuously varying signals.

- Almost all physical quantities (observables) are continuous in nature.

As electronics designers, we know that:

Digital electronics is very *powerful*, *cheap*, and relatively *easy* to design (at least compared to analog circuits).

Digital electronics only works with digital signals.

#### THEREFORE ...

If we're ever going to make anything useful, we need to a way to convert (or approximate) an ANALOG signal to (by) a sequence of digital-binary numbers, and vice versa.

## Analog → Digital

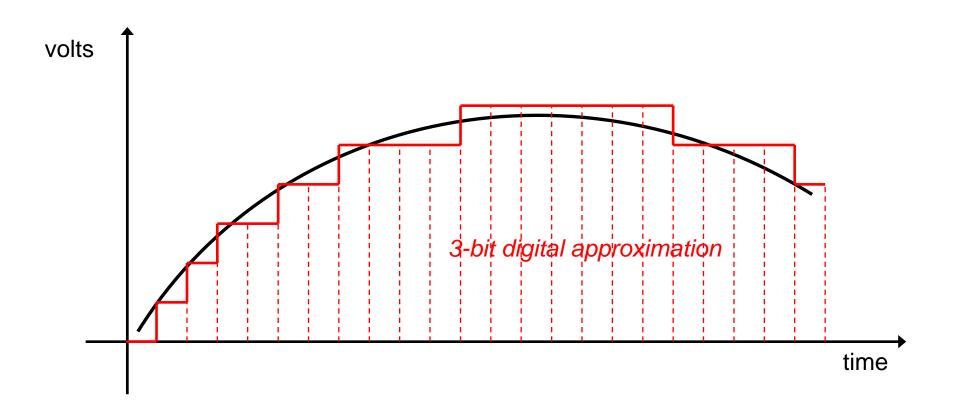

Algorithm: → At each clock cycle, round your analog voltage to the nearest digital value.

→ The size of a digital step is defined by V<sub>ref</sub>/2<sup>n</sup> for an n-bit converter.

## **Shannon-Nyquist Sampling Theorem**

#### THEOREM:

A continuous-time finite bandwidth signal can be exactly reconstructed from its samples if the sampling frequency is greater than 2 times the signal bandwidth B, where B is largest (non-zero) frequency component of the signal.

F=2B is referred to as the Nyquist frequency (the lowest possible sampling frequency).

#### **Practical Considerations:**

> Any finite duration signal has  $B \rightarrow +\infty$ , so exact mathematical application of the theorem is impossible.

> The theorem indicates the frequency scale that one should use in order to usefully sample a signal  $\rightarrow$  always use a sampling rate which is greater than twice the highest frequency component of "reasonable amplitude".

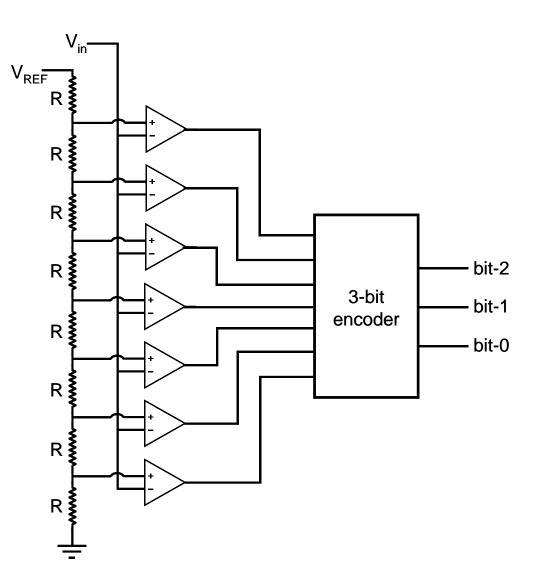

## **Flash ADCs**

The fastest (and most expensive) n-bit ADCs use 2<sup>n</sup>-1 comparators to determine which of the 2<sup>n</sup> numbers the analog input is closest to.

8-bit ADC: 255 comparators.

12-bit ADC: 4096 comparators

In general, higher the bit resolution results in a slower ADC (and more expensive).

Most digital oscilloscopes use an 8-bit ADC.

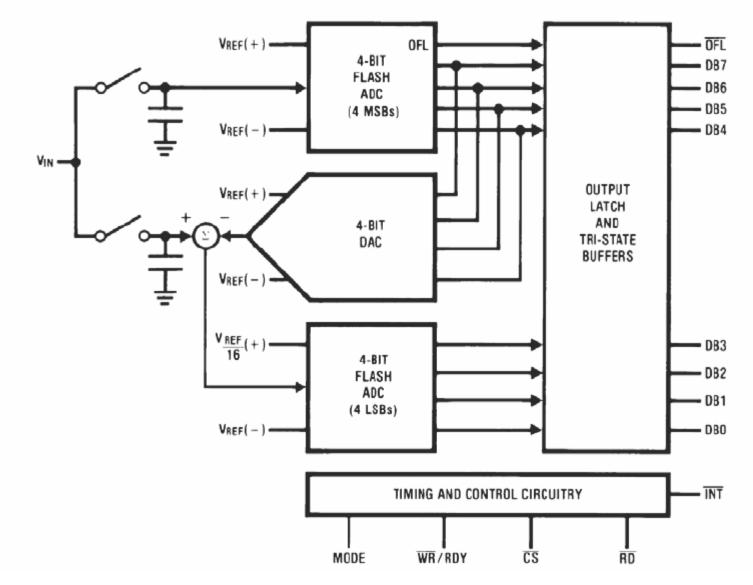

## **ADC0820: Half-Flash ADC (I)**

- In order to keep the number of comparators small, it holds the input voltage, and converts it in steps:

- $\rightarrow$  Converts the upper four bits with a 4-bit ADC.

- → Converts the digitized value back into an analog value with a Digital-to-Analog Converter (DAC).

- → Subtracts this from the input to generate the smaller, difference voltage.

- $\rightarrow$  Finally, it uses a 2<sup>nd</sup> 4-bit ADC to convert the lower 4-bits.

The entire process takes less than 800 ns when operating off the internal timing of the ADC0820 (RD mode).

→ You can run it somewhat faster with some clever timing (WR-RD) mode but we will opt for simplicity.

#### **ADC0820: Half-Flash ADC (II)**

[figure from the National Semiconductor ADC0820 datasheet]

## **ADC0820: Half-Flash ADC (III)**

#### **Functional Table**

| Pin   | Name                | Function                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1     | VIN                 | Analog input; range $GND \le VIN \le VCC$                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 2-5   | DB0-DB3             | TRI-STATE data outputs; bit 0 (LSB) to bit 3                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 6     | WR / RDY            | <ul> <li>WR-RD Mode - WR: With CS low, the conversion is started on the falling edge of WR.</li> <li>RD Mode - RDY: RDY will go low after the falling edge of CS; RDY will go TRI-STATE when the result of the conversion is strobed into the output latch.</li> </ul>                                                                                                                  |  |  |  |

| 7     | MODE                | Select mode: $LOW = RD$ Mode $HIGH = WR-RD$ Mode                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 8     | RD                  | <ul> <li>WR-RD Mode</li> <li>With CS low, the TRI-STATE data outputs (DB0-DB7) will be activated when RD goes low.</li> <li>RD Mode</li> <li>With CS low, the conversion will start with RD going LOW; also RD will enable the TRI-STATE data outputs at the completion of the conversion. RDY going TRI-STATE and INT going low indicates the completion of the conversion.</li> </ul> |  |  |  |

| 9     | INT                 | INT going LOW indicates that the conversion is completed and the data result is in the output latch. INT is reset by rising edge on RD or CS.                                                                                                                                                                                                                                           |  |  |  |

| 11    | V <sub>REF(-)</sub> | Bottom of resistor ladder; range: $GND \leq V_{REF(-)} \leq V_{REF(+)}$                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 12    | V <sub>REF(+)</sub> | Top of resistor ladder; range: $V_{REF(-)} \leq V_{REF(+)} \leq V_{CC}$                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 13    | CS                  | CS must be low for the RD or WR to be recognized.                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 14-17 | DB4-7               | TRI-STATE data output—bits 4-7                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 18    | OFL                 | Overflow—If the analog input is higher than the $V_{REF(+)}$ , OFL will be LOW at the end of conversion. Can be used to cascade.                                                                                                                                                                                                                                                        |  |  |  |

## ADC0820: Half-Flash ADC (IV)

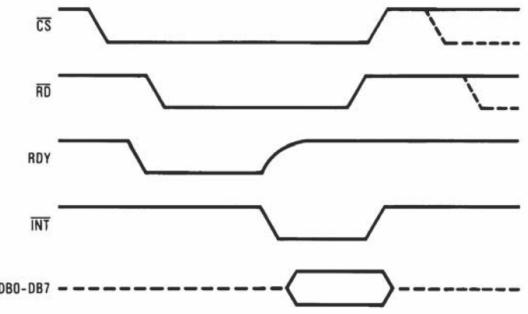

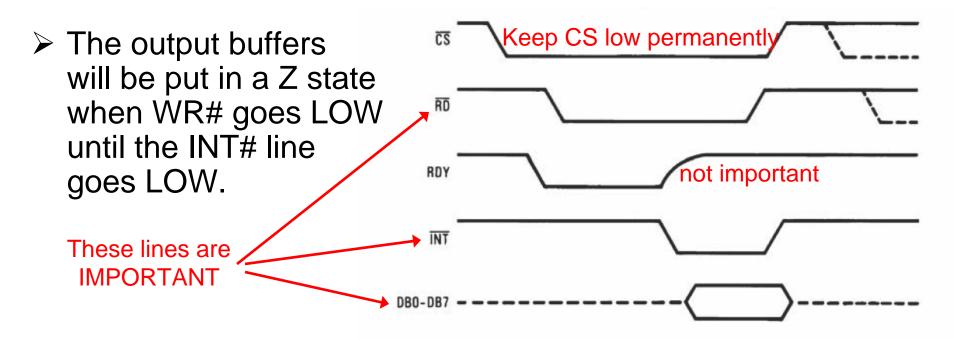

- In RD mode, the RD# line going LOW initiates the conversion.

- When the conversion is complete, the INT# line goes LOW & the data is latched into output buffers.

- The output buffers will be put in a Z state when RDY# goes LOW until the INT# line goes LOW.

[figure from the National Semiconductor ADC0820 datasheet]

## ADC0820: Half-Flash ADC (IV)

- In RD mode, the RD# line going LOW initiates the conversion.

- When the conversion is complete, the INT# line goes LOW & the data is latched into output buffers.

[figure from the National Semiconductor ADC0820 datasheet]

## **Digital → Analog**

A Digital-to-Analog Converter (DAC) is used to convert a digital signal into an analog voltage.

#### A DAC is useful for:

Generating a voltage from a computer, microprocessor, or FPGA that will then control part of an experiment.

Producing a digitally synthesized waveform (triangle, sine, or more complex).

Converting digital music to sound, etc …

(the CD standard is 16-bits at 44.1 KHz)

DACs are generally much faster than ADCs for a same bit resolution.

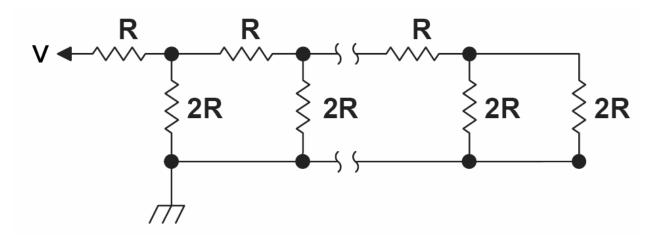

### **R-2R resistor ladder (I)**

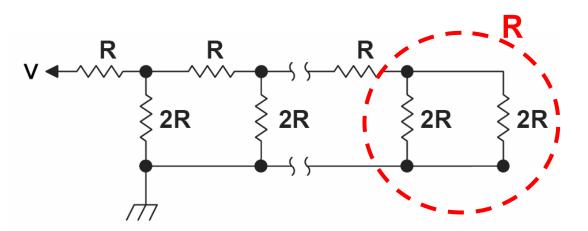

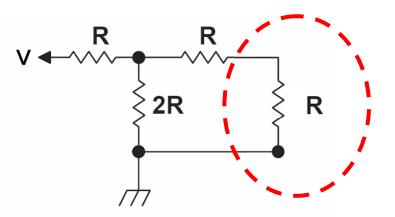

It's easy to make the DAC output voltages.

Look from the right-hand side

- $\rightarrow$  2 parallel resistors

- $\rightarrow$  Each with a value of 2R

### **R-2R resistor ladder (I)**

It's easy to make the DAC output voltages.

Look from the right-hand side

- $\rightarrow$  2 parallel resistors

- $\rightarrow$  Each with a value of 2R

#### **R-2R resistor ladder (II)**

Continuing farther to the left, we find that the effective resistance to ground is *R* at every dot on the top line

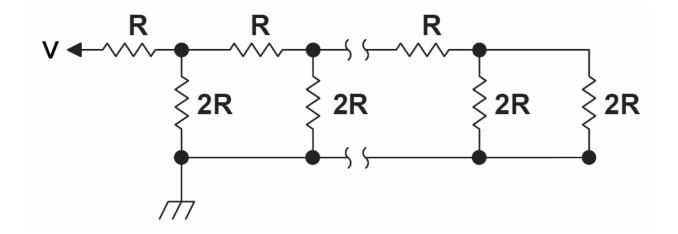

## **R-2R resistor ladder (III)**

- The ladder acts like a series of voltage dividers that reduces the voltage by an additional factor of 2 at each R-2R junction.

- V decreases by half at each connection point along the top rail.

- Thus each output voltage is related to the input voltage by a power of two.

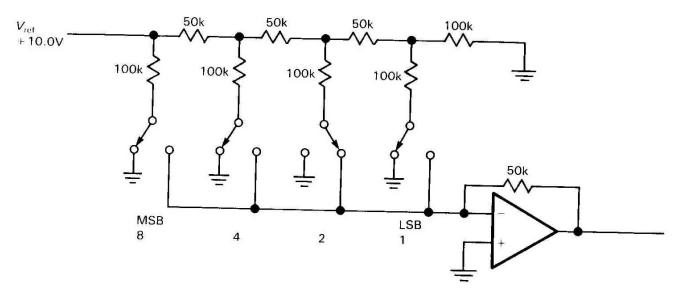

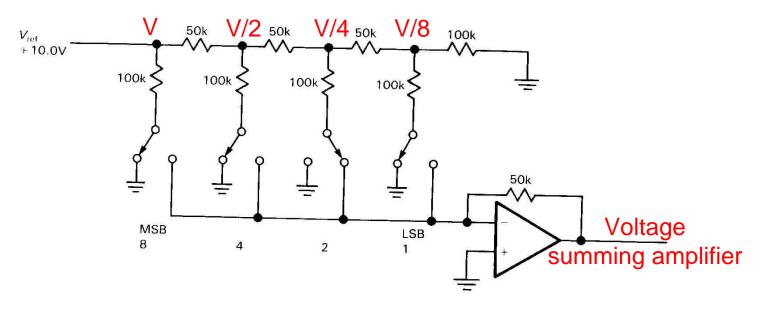

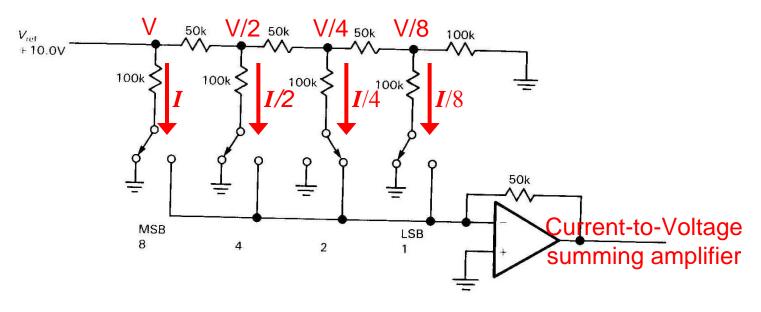

## **Simple DAC**

- We can generate an analog voltage by adding together the voltages represented by the various stages in the ladder.

- If we sum the ladder outputs based on a simple a binary representation in switches then we have a DAC.

[figure from the Art of Electronics (2<sup>nd</sup> edition, 1999) by P. Horowitz and W. Hill, p. 616]

## **Simple DAC**

- We can generate an analog voltage by adding together the voltages represented by the various stages in the ladder.

- If we sum the ladder outputs based on a simple a binary representation in switches then we have a DAC.

[figure from the Art of Electronics (2<sup>nd</sup> edition, 1999) by P. Horowitz and W. Hill, p. 616]

## **Simple DAC**

- We can generate an analog voltage by adding together the voltages represented by the various stages in the ladder.

- If we sum the ladder outputs based on a simple a binary representation in switches then we have a DAC.

[figure from the Art of Electronics (2<sup>nd</sup> edition, 1999) by P. Horowitz and W. Hill, p. 616]

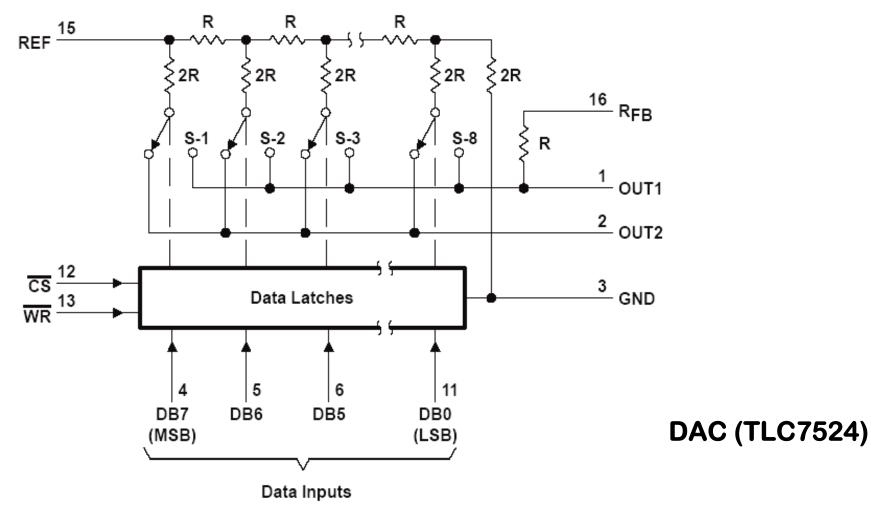

#### A real DAC: the TLC7524

[figure from Texas Instruments TLC7524 datasheet]

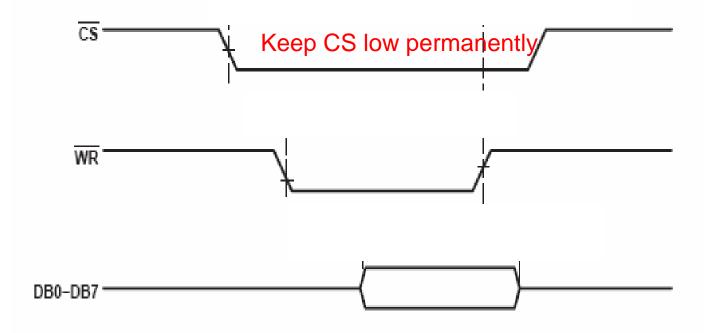

## **TLC7524 timing**

➢ The data on the digital inputs is sent to the analog output when WR goes LOW.

➢ When WR is HIGH, the digital inputs and analog output remain latched to their present values.

[figure from Texas Instruments TLC7524 datasheet]

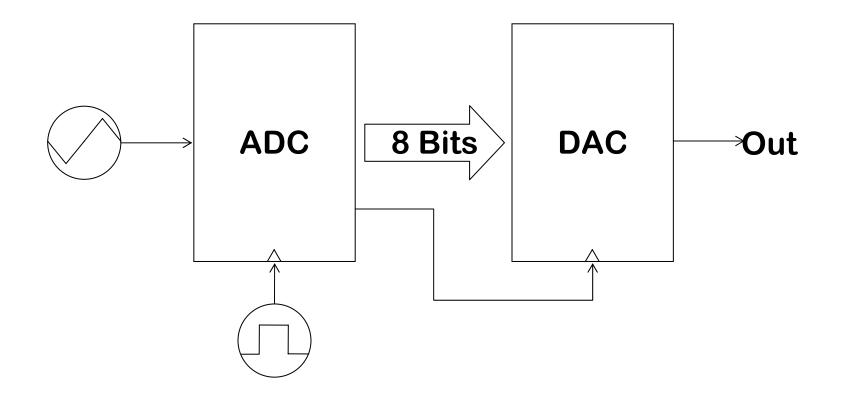

## ADC → DAC Analog-to-Analog

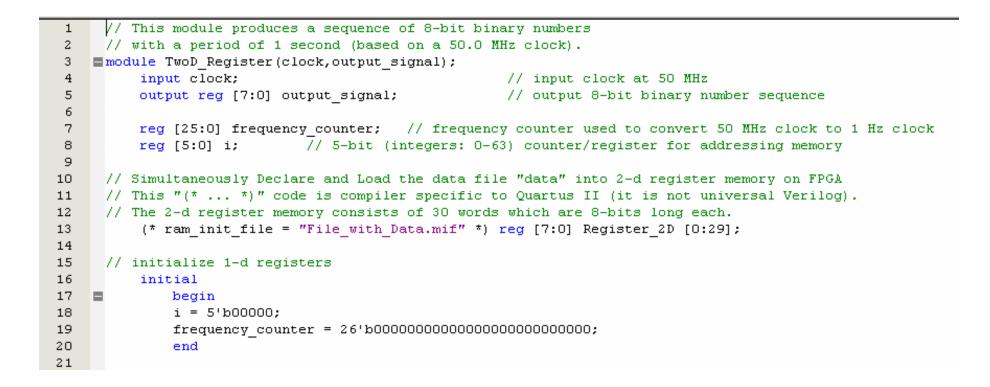

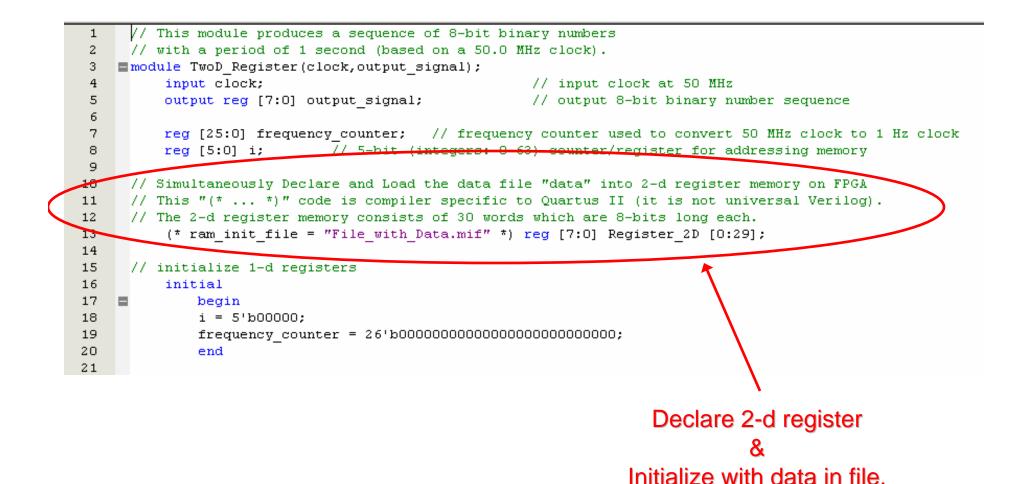

#### **2-dimensional registers with Quartus II**

#### **2-dimensional registers with Quartus II**

### **Using a 2-d Register in Verilog**

```

21

22

// This 50 MHz clock counter counts up to 50e6 in 1 seconds and then resets

// and increases in the "i" counter by 1 ("i" clock is effectively 1 Hz).

23

24

always@(posedge_clock)

25

begin

26

27

// increase 50 MHz frequency counter by 1.

frequency counter <= frequency counter + 1;</pre>

28

29

// if "frequency counter" is equal to 50 million,

30

// then reset frequency counter to ZERO

31

// and send the 8-bit word corresponding to Register 2D[i] to the ouptut

32

// and increase the "i" counter by ONE.

33

if (frequency counter == 26'b1011111010111100001000000)

34

35

begin

36

output signal <= Register 2D[i];</pre>

37

38

i \le i + 5'b00001;

if (i == 5'b10000) i <= 5'b00000; // reset "i" counter to ZERO if it becomes 32.

39

40

end

41

end

42

43

endmodule

```

### **Using a 2-d Register in Verilog**

```

21

22

// This 50 MHz clock counter counts up to 50e6 in 1 seconds and then resets

23

// and increases in the "i" counter by 1 ("i" clock is effectively 1 Hz).

24

always@(posedge clock)

25

begin

26

27

// increase 50 MHz frequency counter by 1.

28

frequency counter <= frequency counter + 1;

29

// if "frequency counter" is equal to 50 million,

30

31

// then reset frequency counter to ZERO

// and send the 8-bit word corresponding to Register 2D[i] to the ouptut

32

33

// and increase the "i" counter by ONE.

if (frequency counter == 26'b1011111010111100001000000)

34

35

begin

36

37

Coutput signal <= Register 2D[i];</pre>

38

i <= 1 + 5'b00001,

if (i == 5'b10000) i <= 5'b00000;

reset "i" counter to ZERO if it becomes 32.

39

40

end

41

end

42

43

endmodule

Reads the 8-bit word at address "i" of "Register_2D"

&

sends it to the 8-bit 1-d register "output_signal".

```

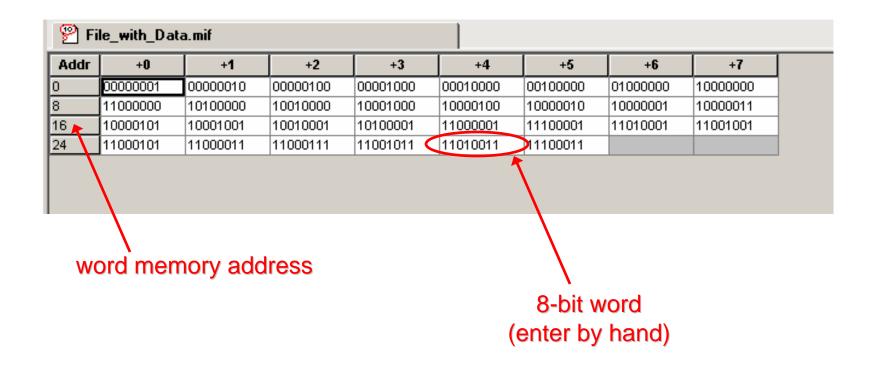

## **Generating the Memory Initialization File (I)**

You can write the file yourself or ...

| 🖡 File_with_Data.mif - Notepad |              |                                                                                                              |      |                                                                                                                          |  |  |  |

|--------------------------------|--------------|--------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| File                           | Edit         | Format                                                                                                       | View | Help                                                                                                                     |  |  |  |

| DED.                           | TH=8<br>TH=3 | <b>);</b>                                                                                                    |      |                                                                                                                          |  |  |  |

|                                |              | _RADI)<br>DIX=B)                                                                                             |      | 5;                                                                                                                       |  |  |  |

| END                            | TENT         | BEGI<br>0<br>12345678910<br>112345678910<br>1123456789<br>1123456789<br>222222222222222222222222222222222222 |      | 00000001;<br>00000100;<br>00001000;<br>00010000;<br>00100000;<br>00100000;<br>0000000;<br>0000000;<br>0000000;<br>000000 |  |  |  |

| 4                              |              |                                                                                                              |      |                                                                                                                          |  |  |  |

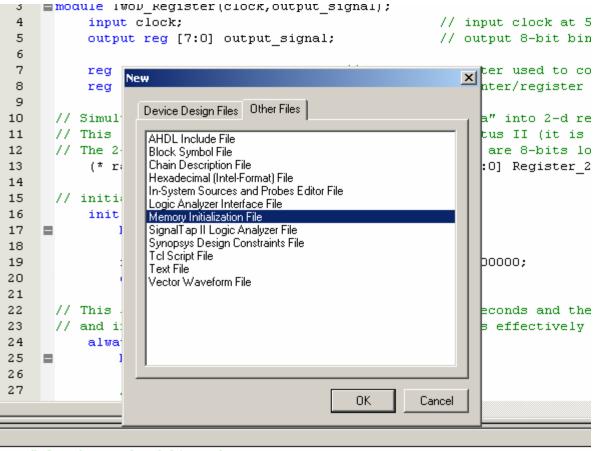

## **Generating the Memory Initialization File (II)**

You can use Quartus II to generate the file using the Memory Editor:

Select: New File

- → Other Files

- → Memory Initialization File

gister" for the top level hierarchy

#### **Memory Initialization File Editor**

Right-click to enter type memory information: integer, hexadecimal, binary, etc ...

## **Logic Element or RAM memory ?**

If your memory space is not very large, the compiler will automatically choose to implement your Verilog circuit with D-type flip-flops of the Logic Elements. You can force the compiler to use the dedicated FPGA memory:

Assignments > Settings >

| ettings >  | Settings - TwoD_Register                                                                                                                                                                                                                                                                                                                                                                                                                 | ×.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ettings >  | Settings - TwoD_Register<br>Category:<br>General<br>Files<br>Libraries<br>Device<br>Operating Settings and Conditions<br>Voltage<br>Temperature<br>Compilation Process Settings<br>Early Timing Estimate<br>Incremental Compilation<br>EDA Tool Settings<br>Fitter Settings<br>Fitter Settings<br>Fitter Settings<br>SignalT ap II Logic Analyzer<br>Logic Analyzer Interface<br>Simulator Settings<br>BowerPlay Power Analyzer Settings | Analysis & Synthesis Settings     Specify options for analysis & synthesis. These options control Quartus II Integrated Synthesis and do not affect VQM or EDIF netlists unless WYSIWYG primitive resynthesis is enabled.     Optimization Technique         Optimization Technique         Speed         Balanced         Area         Ciock         Gutput Enable         Register Control Signals |  |  |

| Click here |                                                                                                                                                                                                                                                                                                                                                                                                                                          | Auto DSP Block Replacement Auto RAM Replacement Auto RAM Replacement Auto RAM Replacement Auto RAM Block Balancing Restructure Multiplexers: Auto PowerPlay power optimization: Normal compilation HDL Message Level: Level2 Advanced More Settings Description: OK Cancel                                                                                                                           |  |  |

## **Logic Element or RAM memory ?**

If your memory space is not very large, the compiler will automatically choose to implement your Verilog circuit with D-type flip-flops of the Logic Elements. You can force the compiler to use the dedicated FPGA memory:

Assignments > Settings >

| ore Analysis & Synthesis Settings                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           | 2                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|

| Specify the settings for the logic options in your<br>entity in the Assignment Editor will override the o                                                                                                                                                                                                                                                                                                                                                   |                                                                           | ndividual node or  |

| Option<br>Name: Allow Any RAM Size For Recog<br>Setting: Off<br>Description:<br>Allows the Compiler to infer RAMs of any size<br>the current minimum requirements.                                                                                                                                                                                                                                                                                          |                                                                           | Reset<br>Reset All |

| Existing option settings:<br>Name:<br>Add Pass-Through Logic to Inferred RAMs                                                                                                                                                                                                                                                                                                                                                                               | Setting:                                                                  | A                  |

| Allow Any RAM Size For Recognition<br>Allow Any ROM Size For Recognition<br>Allow Any ROM Size For Recognition<br>Allow Any Shift Register Size For Recognition<br>Allow Synchronous Control Signals<br>Auto Carry Chains<br>Auto Clock Enable Replacement<br>Auto Open-Drain Pins<br>Auto Open-Drain Pins<br>Auto RAM Replacement<br>Auto RAM to Logic Cell Conversion<br>Auto Resource Sharing<br>Auto ROM Replacement<br>Auto Shift Register Replacement | Off<br>Off<br>Off<br>On<br>On<br>On<br>On<br>On<br>On<br>On<br>Off<br>Off |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OK                                                                        | Cancel             |

## **Dedicated Memory Usage**

Check compiler report for memory usage:

| Flow Status                        | Successful - Mon Oct 22 03:03:49 2007   |    |

|------------------------------------|-----------------------------------------|----|

| Quartus II Version                 | 7.1 Build 156 04/30/2007 SJ Web Edition |    |

| Revision Name                      | TwoD_Register                           |    |

| Top-level Entity Name              | TwoD_Register                           |    |

| Family                             | Cyclone II                              |    |

| Device                             | EP2C35F672C6                            |    |

| Timing Models                      | Final                                   |    |

| Met timing requirements            | N/A                                     |    |

| Total logic elements               | 55                                      |    |

| Total combinational functions      | 55                                      |    |

| Dedicated logic registers          | 31                                      |    |

| Total registers                    | 31 Dedicated Mamanul Jaco               |    |

| Total pins                         | Dedicated Memory Usag                   | je |

| Total virtual pins                 | 0                                       |    |

| Total memory bits                  | 256                                     |    |

| Embedded Multiplier 9-bit elements | 0                                       |    |

| Total PLLs                         | 0                                       |    |