#### **Undergraduate Research**

Today 5-6pm @ Blow 201  $\rightarrow$  Graduate School Fellowships.

Tomorrow 7-8pm @ Blow 201  $\rightarrow$  Summer Research Info Session.

More info on-line at:

http://web.wm.edu/scholarships/

http://physics.wm.edu/~inovikova/StudentResearch/SummerResearch.htm

The summer between Junior and Senior year is the best time to get into an REU summer research program !!!

#### **DSP Project**

#### **Reminder:**

Project proposals are due on Friday, October 9<sup>th</sup> by 5pm.

Budget: \$250/team.

Last year's DSP Design Competition winners Justin Vazquez, Ryan Zielinski, and Jordan Gates

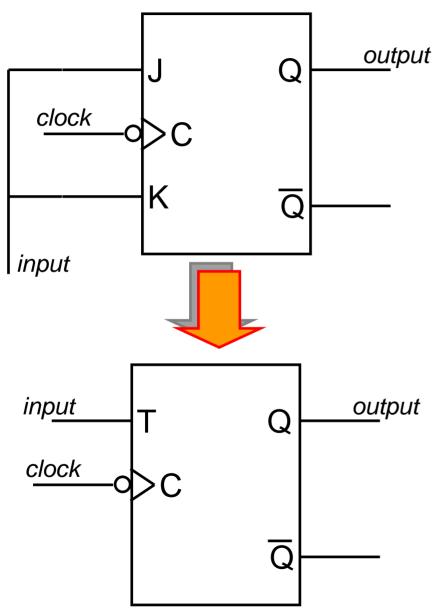

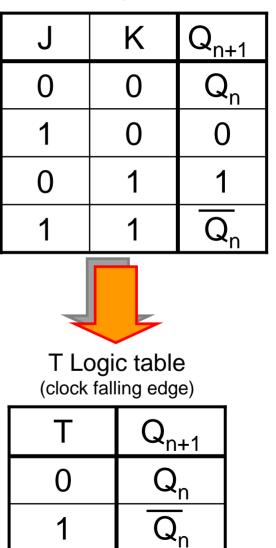

# **T-type flip-flop**

JK Logic table

T-type flip-flops are used in counters.

## **Multiplexers**

#### What's a multiplexer ?

A multiplexer is a generalized multi-input and multi-output gate. It will produce a specific multiple line output for each specific multiple line input.

**Example:** 3-line input and 4-line output (i.e. 3-to-4 multiplexer).

| А | В | С | 1 | 2 | 3 | 4 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

N.B. Multiplexers can be very useful for converting a binary number to a HEX display code.

## **Multiplexers with FPGAs (la)**

You could build a multiplexer out of logic gates using Karnaugh maps ... or you could let the Verilog compiler figure it out.

N-to-1 multiplexer:

mux\_primitive.v

| ſ | 1  | <pre>primitive mux_primitive(out1, A, B, C); // 3-to-1 multiplexer</pre> |

|---|----|--------------------------------------------------------------------------|

|   | 2  | input A, B, C; // 3 input wires                                          |

|   | 3  | output out1; // 1 output wire                                            |

|   | 4  |                                                                          |

|   | 5  | table // table defines the output based on the 3 inputs                  |

|   | 6  | // A B C out1                                                            |

|   | 7  | 000:0;                                                                   |

|   | 8  | 001:0;                                                                   |

|   | 9  | 010:0;                                                                   |

|   | 10 | 100:1;                                                                   |

|   | 11 | 110:1;                                                                   |

|   | 12 | 011:0;                                                                   |

|   | 13 | 101:1;                                                                   |

|   | 14 | 111:0;                                                                   |

|   | 15 | endtable                                                                 |

|   | 16 |                                                                          |

|   | 17 | endprimitive                                                             |

|   | 18 |                                                                          |

|   |    |                                                                          |

# **Multiplexers with FPGAs (IIa)**

An always block with "if" statements can be used for an N-to-M multiplexer:

mux\_always\_if.v

| 1  | module mux always if(input 3bit, output 4bit); // 3-to-4 multiplexer |

|----|----------------------------------------------------------------------|

| 2  | input [2:0] input 3bit; // 3 input lines (bits)                      |

| 3  | output reg [3:0] output 4bit; // 4-bit output register               |

| 4  | Capito leg [olo] Capito_imit, ,, i mito capito legiboli              |

| 5  | // always block with "if" statement for each input case              |

| 6  | always                                                               |

| 7  | begin                                                                |

|    |                                                                      |

| 8  | <pre>if(input_3bit == 3'b000) output_4bit &lt;= 4'b0001;</pre>       |

| 9  | <pre>if(input_3bit == 3'b001) output_4bit &lt;= 4'b0010;</pre>       |

| 10 | if(input_3bit == 3'b010)                                             |

| 11 | if(input 3bit == 3'b100) output 4bit <= 4'b1000;                     |

| 12 | if(input 3bit == 3'b110) output 4bit <= 4'b1100;                     |

| 13 | <pre>if(input 3bit == 3'b011) output 4bit &lt;= 4'b0110;</pre>       |

| 14 | if(input 3bit == 3'b101) output 4bit <= 4'b1010;                     |

| 15 | if(input 3bit == 3'b111) output 4bit <= 4'b0001;                     |

| 16 | end                                                                  |

| 17 | endmodule                                                            |

| 18 |                                                                      |

|    |                                                                      |

An always block guarantees that you won't have any signal races or glitches.

## **Multiplexers with FPGAs (III)**

An always block with "case" constructs can be used for an N-to-M multiplexer:

| 1  | <pre>module mux_always_case(input_3bit,output_4bit); // 3-to-4 multiplexer</pre> |

|----|----------------------------------------------------------------------------------|

| 2  | <pre>input [2:0] input_3bit; // 3-bit input</pre>                                |

| 3  | output reg [3:0] output_4bit; // 4-bit output                                    |

| 4  |                                                                                  |

| 5  | always // always block with "case" construct                                     |

| 6  | E begin                                                                          |

| 7  | <pre>case(input_3bit)</pre>                                                      |

| 8  | 3'b000: output_4bit <= 4'b0001;                                                  |

| 9  | 3'b001: output_4bit <= 4'b0010;                                                  |

| 10 | 3'b010: output_4bit <= 4'b0100;                                                  |

| 11 | 3'b100: output_4bit <= 4'b1000;                                                  |

| 12 | 3'b110: output_4bit <= 4'b1100;                                                  |

| 13 | 3'b011: output_4bit <= 4'b0110;                                                  |

| 14 | 3'b101: output_4bit <= 4'b1010;                                                  |

| 15 | 3'b111: output_4bit <= 4'b0001;                                                  |

| 16 | endcase                                                                          |

| 17 | end                                                                              |

| 18 |                                                                                  |

| 19 | endmodule                                                                        |

|    |                                                                                  |

# **Multiple Modules**

#### multiple\_modules.v

| 1            | module multiple_modules(input_clock, output_       | ut_FourBi      | ts); // top-level module                                                      |

|--------------|----------------------------------------------------|----------------|-------------------------------------------------------------------------------|

| 2            | input input_clock; //                              | ' input w      | ire                                                                           |

| 3            | output [3:0] output_FourBits; //                   | output         | wires                                                                         |

| 4            |                                                    |                |                                                                               |

| 5            | <pre>wire [2:0] counter_output; //</pre>           |                |                                                                               |

| 6            | <pre>wire [2:0] mux_input; //</pre>                | / input w      | ires of multiplexer                                                           |

| 7            |                                                    |                |                                                                               |

| 8            | <pre>assign mux_input = counter_output; //</pre>   | ' connect      | the counter output and multiplexer input wires                                |

| 9            |                                                    |                |                                                                               |

| 10           | counter counter_result(input_clock, co             | ounter_ou      |                                                                               |

| 11           |                                                    |                | <pre>// with instance "counter_result"</pre>                                  |

| 12           |                                                    |                |                                                                               |

| 13           | mux_always_case mux_output(mux_input,              | output_F       | ourBits); // call the "mux_always_case" module                                |

| 14           |                                                    |                | <pre>// with instance " mux_output"</pre>                                     |

| 15           |                                                    |                |                                                                               |

| 16           | endmodule                                          | mux_alway      | s_case.v*                                                                     |

| 17           |                                                    |                |                                                                               |

|              |                                                    | 1              | <pre>module mux_always_case(input_3bit,output_4bit); /</pre>                  |

|              |                                                    | 2              | input [2:0] input_3bit; // 3-bit inpu                                         |

| -tor         |                                                    | 3              | output reg [3:0] output_4bit; // 4-bit outp                                   |

| inter. v     |                                                    | 5              | always // always block with "case" const                                      |

| 1            | <pre>module counter(input clk, output 3bit);</pre> | 6              | always // always block with "case" const begin                                |

| 2            | input input clk;                                   | 7              | case(input 3bit)                                                              |

| 3            | output reg [2:0] output 3bit;                      | 8              | 3'b000: output 4bit <= 4'b0001;                                               |

| 4            |                                                    | 9              | 3'b001: output_4bit <= 4'b0010;                                               |

| 5            | always@(posedge input_clk)                         | 10             | 3'b010: output 4bit <= 4'b0100;                                               |

| 6            | —                                                  | 11             | 3'b100: output 4bit <= 4'b1000;                                               |

| 7            | output_3bit <= output_3bit + 3'b001;               | 12             | 3'b110: output 4bit <= 4'b1100;                                               |

| (            | end                                                | 13             | 3'b011: output 4bit <= 4'b0110;                                               |

| 8            |                                                    |                |                                                                               |

|              |                                                    | 14             | 3'b101: output 4bit <= 4'b1010;                                               |

| 8            | endmodule                                          | 14<br>15       |                                                                               |

| 8<br>9       | endmodule                                          |                | 3'b101: output_4bit <= 4'b1010;<br>3'b111: output_4bit <= 4'b0001;<br>endcase |

| 8<br>9<br>10 | endmodule                                          | 15             | 3'b111: output_4bit <= 4'b0001;                                               |

| 8<br>9<br>10 | endmodule                                          | 15<br>16       | 3'b111: output_4bit <= 4'b0001;<br>endcase                                    |

| 8<br>9<br>10 | endmodule                                          | 15<br>16<br>17 | 3'b111: output_4bit <= 4'b0001;<br>endcase                                    |

# **Multiple Modules**

| <pre>t_FourBits); // top-level module<br/>input wire<br/>output wires<br/>for connecting the 2 lower level modules<br/>output wires of counter<br/>input wires of multiplexer<br/>connect the counter output and multiplexer input wires<br/>unter_output); // call the "counter" module</pre>                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mux_always_case.v*  1 module mux_always_case(input_3bit,output_4bit); // 3- 2 input [2:0] input_3bit; // 3-bit input</pre>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3 output reg [3:0] output_4bit; // 4-bit output<br>4<br>5 always // always block with "case" construct                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6       begin         7       Case(input_3bit)         8       3'b000: output_4bit <= 4'b0001;         9       3'b011: output_4bit <= 4'b0010;         10       3'b010: output_4bit <= 4'b0100;         11       3'b100: output_4bit <= 4'b1000;         12       3'b110: output_4bit <= 4'b1100;         13       3'b101: output_4bit <= 4'b1100;         14       3'b101: output_4bit <= 4'b1010;         15       3'b111: output_4bit <= 4'b0001;         16       endcase         17       end         18       19         19       endmodule |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# **Multiple Modules**

| FourBit<br>nput without                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ts); // top-level module                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g: D(<br>acput with a second seco |                                                                                                                                                                                                                                                                                                                                                                                             |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ourBits); // call the "mux_always_case" module<br>// with instance " mux_output"<br>s_case.v*                                                                                                                                                                                                                                                                                               |

| 2<br>3<br>4<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <pre>input [2:0] input_3bit; // 3-bit input<br/>output reg [3:0] output_4bit; // 4-bit output<br/>always // always block with "case" construct</pre>                                                                                                                                                                                                                                        |

| 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>begin     case(input_3bit)     3'b000: output_4bit &lt;= 4'b0001;     3'b001: output_4bit &lt;= 4'b0010;     3'b010: output_4bit &lt;= 4'b0100;     3'b100: output_4bit &lt;= 4'b1000;     3'b110: output_4bit &lt;= 4'b1100;     3'b011: output_4bit &lt;= 4'b0110;     3'b101: output_4bit &lt;= 4'b1010;     3'b111: output_4bit &lt;= 4'b0001;     endcase     end endmodule</pre> |

| .)<br>:()<br>.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nput w<br>onnect<br>ter_ou<br>tput_F<br><b>Jx_alway</b><br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18                                                                                                                                                                                                                                  |